**Documentation**

# KL5151/KS5151, KL5152/KS5152

**Incremental Encoder Terminals**

Version: 2.0.0

Date: 2016-03-15

# 1 Product overview: incremental encoder interface

Version: 2.0.0

<u>KL5151-0000 [▶ 8]</u>: single-channel incremental encoder terminal

KL5151-0021 [▶ 9]: single-channel incremental encoder terminal with comparator output

KL5151-0050 [▶ 10]: two-channel incremental encoder terminal

KL5152-0000 [▶ 10]: two-channel incremental encoder terminal

# **Table of contents**

| 1 | Prod | uct ove        | rview: incremental encoder interface   | 3  |

|---|------|----------------|----------------------------------------|----|

| 2 | Fore | word           |                                        | 5  |

|   | 2.1  | Notes          | on the documentation                   | 5  |

|   | 2.2  | Safety         | instructions                           | 6  |

|   | 2.3  | Docum          | nentation issue status                 | 7  |

| 3 | Prod | uct ove        | rview                                  | 8  |

|   | 3.1  |                | 1-0000 - Introduction                  |    |

|   | 3.2  | KL515          | 1-0021 - Introduction                  | 9  |

|   | 3.3  | KL515          | 2-0000 (KL5151-0050) - Introduction    | 10 |

|   | 3.4  | Techni         | cal data                               | 11 |

| 4 | Mour | nting an       | d wiring                               | 12 |

|   | 4.1  |                | ation on mounting rails                |    |

|   | 4.2  |                | ction system                           |    |

|   | 4.3  |                | 1-0000 - Connection                    |    |

|   | 4.4  | KL515          | 1-0021 - Connection                    | 19 |

|   | 4.5  | KL515          | 2-0000 (KL5151-0050) - Connection      | 20 |

|   | 4.6  | ATEX           | - Special conditions                   | 21 |

|   | 4.7  | ATEX           | Documentation                          | 22 |

| 5 | Conf | iguratio       | on software KS2000                     | 23 |

|   | 5.1  | KS200          | 0 - Introduction                       | 23 |

|   | 5.2  | Param          | eterization with KS2000                | 25 |

|   | 5.3  | Setting        | JS                                     | 26 |

| 6 | Acce | ss from        | ı the user program                     | 28 |

|   | 6.1  |                | 1-0000                                 |    |

|   |      | 6.1.1          | Process image                          | 28 |

|   |      | 6.1.2<br>6.1.3 | Control and status bytes               |    |

|   | 6.2  |                | 1-0021                                 |    |

|   | 0.2  | 6.2.1          | Process image                          | 33 |

|   |      | 6.2.2          | Control and status bytes               |    |

|   | 6.3  | KL515          | 2-0000 (KL5150-0050)                   |    |

|   |      | 6.3.2          | Control and status bytes               |    |

|   |      | 6.3.3          | Mapping                                |    |

|   | 6.4  | _              | er                                     |    |

|   |      | 6.4.1<br>6.4.2 | Register overview Register description |    |

|   |      | 6.4.3          | Examples of Register Communication     |    |

| 7 | Appe | ndix           |                                        | 51 |

|   |      |                | rt and Sarvice                         | 51 |

# 2 Foreword

#### 2.1 Notes on the documentation

#### Intended audience

This description is only intended for the use of trained specialists in control and automation engineering who are familiar with the applicable national standards.

It is essential that the following notes and explanations are followed when installing and commissioning these components.

The responsible staff must ensure that the application or use of the products described satisfy all the requirements for safety, including all the relevant laws, regulations, guidelines and standards.

#### Disclaimer

The documentation has been prepared with care. The products described are, however, constantly under development. For that reason the documentation is not in every case checked for consistency with performance data, standards or other characteristics. In the event that it contains technical or editorial errors, we retain the right to make alterations at any time and without warning. No claims for the modification of products that have already been supplied may be made on the basis of the data, diagrams and descriptions in this documentation.

#### **Trademarks**

Beckhoff®, TwinCAT®, EtherCAT®, Safety over EtherCAT®, TwinSAFE®, XFC® and XTS® are registered trademarks of and licensed by Beckhoff Automation GmbH.

Other designations used in this publication may be trademarks whose use by third parties for their own purposes could violate the rights of the owners.

#### **Patent Pending**

The EtherCAT Technology is covered, including but not limited to the following patent applications and patents: EP1590927, EP1789857, DE102004044764, DE102007017835 with corresponding applications or registrations in various other countries.

The TwinCAT Technology is covered, including but not limited to the following patent applications and patents: EP0851348, US6167425 with corresponding applications or registrations in various other countries.

EtherCAT® is registered trademark and patented technology, licensed by Beckhoff Automation GmbH, Germany

#### Copyright

© Beckhoff Automation GmbH & Co. KG, Germany.

The reproduction, distribution and utilization of this document as well as the communication of its contents to others without express authorization are prohibited.

Version: 2.0.0

Offenders will be held liable for the payment of damages. All rights reserved in the event of the grant of a patent, utility model or design.

# 2.2 Safety instructions

#### Safety regulations

Please note the following safety instructions and explanations! Product-specific safety instructions can be found on following pages or in the areas mounting, wiring, commissioning etc.

#### **Exclusion of liability**

All the components are supplied in particular hardware and software configurations appropriate for the application. Modifications to hardware or software configurations other than those described in the documentation are not permitted, and nullify the liability of Beckhoff Automation GmbH & Co. KG.

#### Personnel qualification

This description is only intended for trained specialists in control, automation and drive engineering who are familiar with the applicable national standards.

#### **Description of symbols**

In this documentation the following symbols are used with an accompanying safety instruction or note. The safety instructions must be read carefully and followed without fail!

#### Serious risk of injury!

Failure to follow the safety instructions associated with this symbol directly endangers the life and health of persons.

#### Risk of injury!

Failure to follow the safety instructions associated with this symbol endangers the life and health of persons.

#### Personal injuries!

Failure to follow the safety instructions associated with this symbol can lead to injuries to persons.

**Attention**

#### Damage to the environment or devices

Failure to follow the instructions associated with this symbol can lead to damage to the environment or equipment.

Note

#### Tip or pointer

This symbol indicates information that contributes to better understanding.

# 2.3 Documentation issue status

| Version | Comment                                                                                                                      |

|---------|------------------------------------------------------------------------------------------------------------------------------|

| 2.0.0   | Migration                                                                                                                    |

|         | Update revision status                                                                                                       |

| 1.3.0   | Technical data updated                                                                                                       |

|         | ATEX notes added                                                                                                             |

|         | Extended temperature range for KL5151-0000                                                                                   |

|         | <ul> <li>Description of control and status bytes of the KL5151-0021 corrected</li> </ul>                                     |

| 1.2.0   | Introduction updated                                                                                                         |

|         | <ul> <li>Description of the parameterization of the KL5151 by means of KS2000<br/>configuration software updated.</li> </ul> |

|         | Register description updated                                                                                                 |

|         | Mounting description expanded                                                                                                |

|         | KL5151-0021 added                                                                                                            |

|         | <ul> <li>KL5151-0050 now available as KL5152-0000</li> </ul>                                                                 |

| 1.1.0   | Description of the process images expanded                                                                                   |

|         | Mapping tables added                                                                                                         |

| 1.0     | KL5151-0050 added                                                                                                            |

|         | <ul> <li>Description of the parameterization of the KL5151 by means of KS2000<br/>configuration software added.</li> </ul>   |

| 0.1     | Preliminary version (KL5151-0000 only)                                                                                       |

#### Firmware and hardware versions

| Documentation | KL5151-0000 |          | KL5151-0021 |          | KL5152-0000 (KL5151-0050) |          |

|---------------|-------------|----------|-------------|----------|---------------------------|----------|

| Version       | Firmware    | Hardware | Firmware    | Hardware | Firmware                  | Hardware |

| 2.0.0         | 4E          | 09       | 14          | 08       | 4E                        | 09       |

| 1.3.0         | 4C          | 07       | 13          | 07       | 4C                        | 07       |

| 1.2.0         | 4C          | 07       | 13          | 07       | 4C                        | 07       |

| 1.1.0         | 3A          | 02       | -           | -        | 3A                        | 02       |

| 1.0           | 3A          | 02       |             |          | 3A                        | 02       |

| 0.1           | 3A          | 00       |             |          | -                         | -        |

The firmware and hardware versions (delivery state) can be taken from the serial number printed on the side of the terminal.

Version: 2.0.0

#### Syntax of the serial number

Structure of the serial number: WW YY FF HH

WW - week of production (calendar week)

YY - year of production FF - firmware version HH - hardware version

Example with ser. no.: 35 04 3A 02:

35 - week of production 35 04 - year of production 2004 3A - firmware version 3A 02 - hardware version 02

#### 3 **Product overview**

#### KL5151-0000 - Introduction 3.1

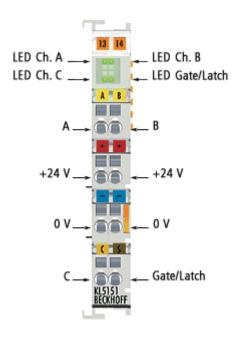

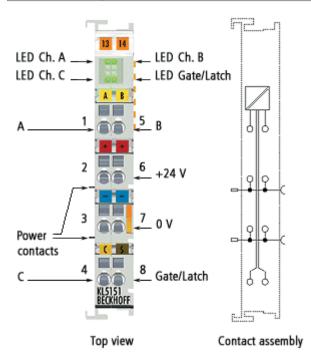

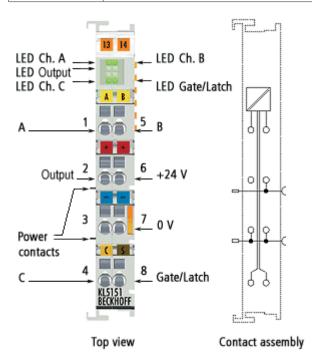

Fig. 1: KL5151

The KL5151-0000 Bus Terminal is an interface with 24 V inputs for the direct connection of incremental encoders. A 32 bit counter with a quadrature decoder and a 32 bit latch for the zero pulse can be read, set or enabled.

The KL5151-0000 Bus Terminal can also be used as a 32-bit up/down counter.

Table 1: LED indicators

| LED          | Function                                                    |

|--------------|-------------------------------------------------------------|

| Ch. A        | Lights up when a signal is present at input A.              |

| Ch. B        | Lights up when a signal is present at input B.              |

| Ch. C        | Lights up when a signal is present at input C (zero input). |

| Gate / Latch | Lights up when a signal is present at the gate/latch input. |

## 3.2 KL5151-0021 - Introduction

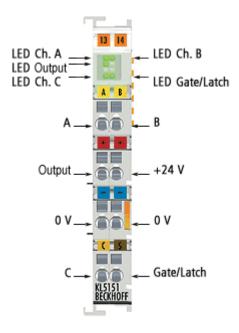

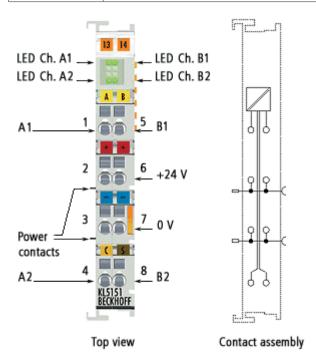

Fig. 2: KL5151-0021

The KL5151-0021 Bus Terminal is an interface with 24 V inputs for the direct connection of incremental encoders. A 32 bit counter with a quadrature decoder and a 32 bit latch for the zero pulse can be read, set or enabled.

The KL5151-0021 Bus Terminal has an additional comparator output.

Table 2: LED indicators

| LED          | Function                                                    |

|--------------|-------------------------------------------------------------|

| Ch. A        | Lights up when a signal is present at input A.              |

| Output       | Lights up when the comparator output is switched on.        |

| Ch. B        | Lights up when a signal is present at input B.              |

| Ch. C        | Lights up when a signal is present at input C (zero input). |

| Gate / Latch | Lights up when a signal is present at the gate/latch input. |

#### Operation

#### Referencing

Enter the reference value for referencing via the output double word <u>DataOUT1 [ $\triangleright$  33]</u> and set bits <u>CB1.0</u> [ $\triangleright$  33] (EnLatchC) and <u>CB1.2 [ $\triangleright$  33]</u> (SetCnt) in the control byte. The reference value is now adopted by the counter on a rising edge at input C.

#### Measuring the workpiece

At the beginning of the measurement the filter value is preset in the filter register  $R0 \ [\triangleright \ 45]$ . Then set the release bit  $CB1.1 \ [\triangleright \ 33]$  (EnMeas) in the control byte. If a plate has been successfully measured, the terminal sets bit  $SB1.1 \ [\triangleright \ 34]$  (MeasDone) in the status byte.

The measurement begins on an appropriate edge. If the level already exists, only the position of the end of the board is determined. The start of the measurement is then taken as the start of the board.

Version: 2.0.0

#### **Post-forming sawing**

The output has a rise time of 10 µs and a 40 µs delay due to the optocoupler.

# 3.3 KL5152-0000 (KL5151-0050) - Introduction

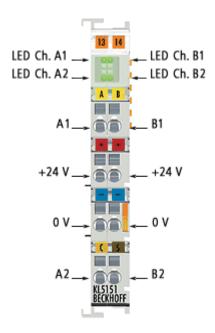

Fig. 3: KL5151-0050

The KL5152-0000 (KL5151-0050) Bus Terminal is an interface with 24 V inputs for the direct connection of two incremental encoders. The terminal can optionally be used as a single-channel or two-channel device.

Table 3: LED indicators

| Signal LED | Function                                        | Encoder |

|------------|-------------------------------------------------|---------|

| Ch. A1     | Lights up when a signal is present at input A1. | 1       |

| Ch. B1     | Lights up when a signal is present at input B1. |         |

| Ch. A2     | Lights up when a signal is present at input A2. | 2       |

| Ch. B2     | Lights up when a signal is present at input B2. |         |

#### **Technical data** 3.4

| Technical data                                         | KL5151-0000                                                          | KL5151-0021            | KL5152-0000 (K                                      | (L5151-0050)                     |  |

|--------------------------------------------------------|----------------------------------------------------------------------|------------------------|-----------------------------------------------------|----------------------------------|--|

| Sensor inputs (channels)                               | 1                                                                    |                        | 2                                                   |                                  |  |

| Encoder connection                                     | A, B, C, Gate, 24 V                                                  |                        | Channel 1: A1, B1<br>Channel 2: A2, B2              |                                  |  |

| Encoder operating voltage                              | 24 V <sub>DC</sub>                                                   |                        |                                                     |                                  |  |

| Counter                                                | 1 x 32 bit binary                                                    |                        | 2 x 32 bit binary                                   |                                  |  |

| Limit frequency                                        | 100 kHz                                                              |                        |                                                     |                                  |  |

| Quadrature decoder                                     | 4-fold evaluation                                                    |                        |                                                     |                                  |  |

| Commands                                               | read, set, latching,<br>Compare function for s                       | setting the output (Kl | _5151-0021 only)                                    |                                  |  |

| Supply voltage                                         | 24 V <sub>DC</sub> (-15%/+20%)                                       |                        |                                                     |                                  |  |

| Comparator output                                      | 0                                                                    | 1                      | 0                                                   |                                  |  |

| Current consumption from the power contacts            | Typically 100 mA (with                                               | out sensor load curr   | ent)                                                |                                  |  |

| Bit width in the K-bus I/O                             | 4 x 16 bit user data, 1                                              | x 8 bit control/status |                                                     |                                  |  |

| Bit width in the input                                 | 2 data words,                                                        |                        | compact [▶ 36]                                      | complete [▶ 36]                  |  |

| process image                                          | 1 status byte                                                        |                        | 4 data words                                        | 4 data words,<br>2 status bytes  |  |

| Bit width in the output process image                  | 2 data words,<br>1 control byte                                      |                        | 2 data words,<br>2 control bytes,<br>2 filler bytes | 4 data words,<br>2 control bytes |  |

| Power supply for electronic                            | via the K-bus                                                        |                        | •                                                   |                                  |  |

| Current consumption from K-bus                         | typically 50 mA                                                      |                        |                                                     |                                  |  |

| Weight                                                 | approx. 50 g                                                         |                        |                                                     |                                  |  |

| Dimensions (W x H x D)                                 | approx. 15 mm x 100 r                                                | mm x 70 mm             |                                                     |                                  |  |

| Mountin [▶ 12]g                                        | on 35 mm mounting ra                                                 | il conforms to EN 60   | 715                                                 |                                  |  |

| Pluggable wiring [▶ 14]                                | at all KSxxxx series ter                                             | minals                 |                                                     |                                  |  |

| Permissible ambient temperature range during operation | -25°C +60°C*<br>0°C +55°C (UL)<br>0°C +55°C ( <u>ATEX</u><br>[▶ 21]) | 0°C + 55°C             |                                                     |                                  |  |

| Permissible ambient temperature range during storage   | -40°C + 85°C                                                         | -25°C + 85°C           |                                                     |                                  |  |

| Permissible relative humidity                          | 95%, no condensation                                                 |                        |                                                     |                                  |  |

| Vibration/shock resistance                             | e conforms to EN 60068-2-6 / EN 60068-2-27                           |                        |                                                     |                                  |  |

| EMC immunity/emission                                  | conforms to EN 61000-6-2 / EN 61000-6-4                              |                        |                                                     |                                  |  |

| Protection class                                       | IP20                                                                 |                        |                                                     |                                  |  |

| Installation position                                  | variable                                                             |                        |                                                     |                                  |  |

| Approval                                               | CE, cULus, ATEX [▶ 21                                                | ]                      |                                                     |                                  |  |

<sup>\*) -25°</sup>C ... +60°C (extended temperature range) 0°C ... +55°C (according to cULus for Canada and the USA) 0°C ... +55°C (according to ATEX, see special conditions)

# 4 Mounting and wiring

# 4.1 Installation on mounting rails

#### Risk of electric shock and damage of device!

Bring the bus terminal system into a safe, powered down state before starting installation, disassembly or wiring of the Bus Terminals!

#### **Assembly**

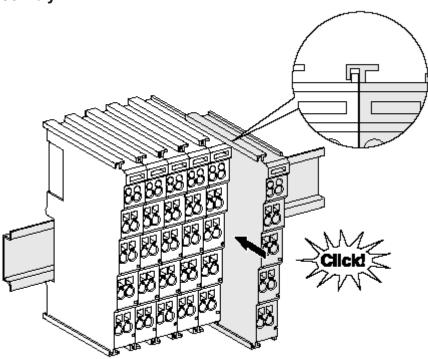

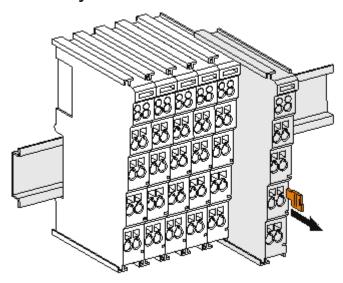

Fig. 4: Attaching on mounting rail

The Bus Coupler and Bus Terminals are attached to commercially available 35 mm mounting rails (DIN rails according to EN 60715) by applying slight pressure:

- 1. First attach the Fieldbus Coupler to the mounting rail.

- 2. The Bus Terminals are now attached on the right-hand side of the Fieldbus Coupler. Join the components with tongue and groove and push the terminals against the mounting rail, until the lock clicks onto the mounting rail.

If the Terminals are clipped onto the mounting rail first and then pushed together without tongue and groove, the connection will not be operational! When correctly assembled, no significant gap should be visible between the housings.

#### Fixing of mounting rails

Note

The locking mechanism of the terminals and couplers extends to the profile of the mounting rail. At the installation, the locking mechanism of the components must not come into conflict with the fixing bolts of the mounting rail. To mount the mounting rails with a height of 7.5 mm under the terminals and couplers, you should use flat mounting connections (e.g. countersunk screws or blind rivets).

#### Disassembly

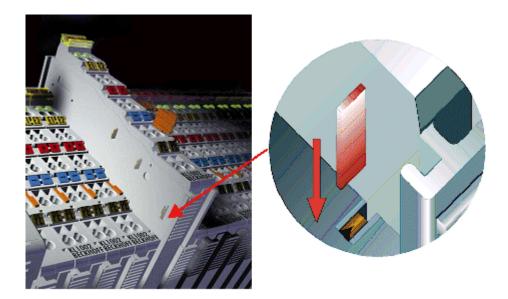

Fig. 5: Disassembling of terminal

Each terminal is secured by a lock on the mounting rail, which must be released for disassembly:

- 1. Pull the terminal by its orange-colored lugs approximately 1 cm away from the mounting rail. In doing so for this terminal the mounting rail lock is released automatically and you can pull the terminal out of the bus terminal block easily without excessive force.

- 2. Grasp the released terminal with thumb and index finger simultaneous at the upper and lower grooved housing surfaces and pull the terminal out of the bus terminal block.

#### Connections within a bus terminal block

The electric connections between the Bus Coupler and the Bus Terminals are automatically realized by joining the components:

- The six spring contacts of the K-Bus/E-Bus deal with the transfer of the data and the supply of the Bus Terminal electronics.

- The power contacts deal with the supply for the field electronics and thus represent a supply rail within

the bus terminal block. The power contacts are supplied via terminals on the Bus Coupler (up to 24 V)

or for higher voltages via power feed terminals.

#### **Power Contacts**

Note

During the design of a bus terminal block, the pin assignment of the individual Bus Terminals must be taken account of, since some types (e.g. analog Bus Terminals or digital 4-channel Bus Terminals) do not or not fully loop through the power contacts. Power Feed Terminals (KL91xx, KL92xx or EL91xx, EL92xx) interrupt the power contacts and thus represent the start of a new supply rail.

#### PE power contact

The power contact labeled PE can be used as a protective earth. For safety reasons this contact mates first when plugging together, and can ground short-circuit currents of up to 125 A.

Fig. 6: Power contact on left side

#### Possible damage of the device

Note that, for reasons of electromagnetic compatibility, the PE contacts are capacitatively coupled to the mounting rail. This may lead to incorrect results during insulation testing or to damage on the terminal (e.g. disruptive discharge to the PE line during insulation testing of a consumer with a nominal voltage of 230 V). For insulation testing, disconnect the PE supply line at the Bus Coupler or the Power Feed Terminal! In order to decouple further feed points for testing, these Power Feed Terminals can be released and pulled at least 10 mm from the group of terminals.

#### Risk of electric shock!

The PE power contact must not be used for other potentials!

# 4.2 Connection system

#### Risk of electric shock and damage of device!

Bring the bus terminal system into a safe, powered down state before starting installation, disassembly or wiring of the Bus Terminals!

#### Overview

The Bus Terminal system offers different connection options for optimum adaptation to the respective application:

- The terminals of KLxxxx and ELxxxx series with standard wiring include electronics and connection level in a single enclosure.

- The terminals of KSxxxx and ESxxxx series feature a pluggable connection level and enable steady wiring while replacing.

Version: 2.0.0

• The High Density Terminals (HD Terminals) include electronics and connection level in a single enclosure and have advanced packaging density.

#### Standard wiring

Fig. 7: Standard wiring

The terminals of KLxxxx and ELxxxx series have been tried and tested for years. They feature integrated screwless spring force technology for fast and simple assembly.

#### Pluggable wiring

Fig. 8: Pluggable wiring

The terminals of KSxxxx and ESxxxx series feature a pluggable connection level.

The assembly and wiring procedure for the KS series is the same as for the KLxxxx and ELxxxx series. The KS/ES series terminals enable the complete wiring to be removed as a plug connector from the top of the housing for servicing.

The lower section can be removed from the terminal block by pulling the unlocking tab.

Insert the new component and plug in the connector with the wiring. This reduces the installation time and eliminates the risk of wires being mixed up.

The familiar dimensions of the terminal only had to be changed slightly. The new connector adds about 3 mm. The maximum height of the terminal remains unchanged.

A tab for strain relief of the cable simplifies assembly in many applications and prevents tangling of individual connection wires when the connector is removed.

Conductor cross sections between 0.08 mm<sup>2</sup> and 2.5 mm<sup>2</sup> can continue to be used with the proven spring force technology.

The overview and nomenclature of the product names for KSxxxx and ESxxxx series has been retained as known from KLxxxx and ELxxxx series.

#### **High Density Terminals (HD Terminals)**

Fig. 9: High Density Terminals

The Bus Terminals from these series with 16 connection points are distinguished by a particularly compact design, as the packaging density is twice as large as that of the standard 12 mm Bus Terminals. Massive conductors and conductors with a wire end sleeve can be inserted directly into the spring loaded terminal point without tools.

#### Wiring HD Terminals

The High Density (HD) Terminals of the KLx8xx and ELx8xx series doesn't support steady wiring.

Note

#### Ultrasonically "bonded" (ultrasonically welded) conductors

#### Ultrasonically "bonded" conductors

It is also possible to connect the Standard and High Density Terminals with ultrasonically "bonded" (ultrasonically welded) conductors. In this case, please note the tables concerning the <u>wire-size width [> 16]</u> below!

#### Wiring

# Terminals for standard wiring ELxxxx / KLxxxx and terminals for steady wiring ESxxxx / KSxxxx

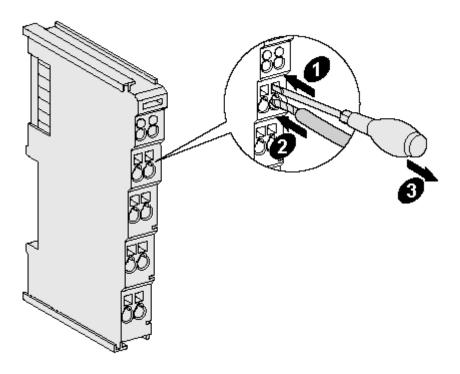

Fig. 10: Mounting a cable on a terminal connection

Up to eight connections enable the connection of solid or finely stranded cables to the Bus Terminals. The terminals are implemented in spring force technology. Connect the cables as follows:

- 1. Open a spring-loaded terminal by slightly pushing with a screwdriver or a rod into the square opening above the terminal.

- 2. The wire can now be inserted into the round terminal opening without any force.

- 3. The terminal closes automatically when the pressure is released, holding the wire securely and permanently.

| Terminal housing      | ELxxxx, KLxxxx           | ESxxxx, KSxxxx           |  |

|-----------------------|--------------------------|--------------------------|--|

| Wire size width       | 0.08 2,5 mm <sup>2</sup> | 0.08 2.5 mm <sup>2</sup> |  |

| Wire stripping length | 8 9 mm                   | 9 10 mm                  |  |

#### High Density Terminals ELx8xx, KLx8xx (HD)

The conductors of the HD Terminals are connected without tools for single-wire conductors using the direct plug-in technique, i.e. after stripping the wire is simply plugged into the contact point. The cables are released, as usual, using the contact release with the aid of a screwdriver. See the following table for the suitable wire size width.

| Terminal housing                                     | High Density Housing                 |

|------------------------------------------------------|--------------------------------------|

| Wire size width (conductors with a wire end sleeve)  | 0.14 0.75 mm <sup>2</sup>            |

| Wire size width (single core wires)                  | 0.08 1.5 mm <sup>2</sup>             |

| Wire size width (fine-wire conductors)               | 0.25 1.5 mm <sup>2</sup>             |

| Wire size width (ultrasonically "bonded" conductors) | only 1.5 mm <sup>2</sup> (see notice |

|                                                      | [ <u>▶ 16]</u> !)                    |

| Wire stripping length                                | 8 9 mm                               |

Version: 2.0.0

#### **Shielding**

#### **Shielding**

Analog sensors and actors should always be connected with shielded, twisted paired wires.

# 4.3 KL5151-0000 - Connection

#### Risk of injury through electric shock and damage to the device!

Bring the Bus Terminals system into a safe, de-energized state before starting mounting, disassembly or wiring of the Bus Terminals.

Fig. 11: KL5151-0000

#### Pin assignment

| Terminal point | No. | In the encoder interface operating mode* Connection for                                                                                                                                                 | In the counter operating mode* Connection for              |  |

|----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|

| A              | 1   | Input A                                                                                                                                                                                                 | Counter input                                              |  |

| +24 V          | 2   | Power contact +24 V (internally connected to terminal point 6)                                                                                                                                          |                                                            |  |

| 0 V            | 3   | Power contact 0 V (internally connected to terminal point 7)                                                                                                                                            |                                                            |  |

| С              | 4   | Input C or zero input (in case bit 0 (EnLatchC [> 29]) is set in the control byte, a rising edge at this input causes the current counter value to be saved in the latch register as a reference mark). | Counter enable (gate input for the counter operating mode) |  |

| В              | 5   | Input B                                                                                                                                                                                                 | Counting direction (high = down, low = up)                 |  |

| +24 V          | 6   | Power contact +24 V (internally connected to terminal point 2)                                                                                                                                          |                                                            |  |

| 0 V            | 7   | Power contact 0 V (internally connected to terminal point 3)                                                                                                                                            |                                                            |  |

| Gate/Latch     | 8   | Gate input or Latch input: if  • bit 3 (EnLatchRise [▶ 29]) is set in the control byte, a rising edge                                                                                                   | no function                                                |  |

|                |     | <ul> <li>bit 4 (<u>EnLatchFall [▶ 29]</u>) is set in the control byte, a falling<br/>edge</li> </ul>                                                                                                    |                                                            |  |

|                |     | at this input causes the current counter value to be saved in the latch register as a reference mark.                                                                                                   |                                                            |  |

<sup>\*)</sup> The operating mode is set with bit R32.15 [▶ 46] of the feature register.

# 4.4 KL5151-0021 - Connection

# WARNING

#### Risk of injury through electric shock and damage to the device!

Bring the Bus Terminals system into a safe, de-energized state before starting mounting, disassembly or wiring of the Bus Terminals.

Fig. 12: KL5151-0021

#### Pin assignment

| Terminal point | No. | Connection for                                                                                                                                                                                |

|----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A              | 1   | Input A                                                                                                                                                                                       |

| Output         | 2   | Comparator output                                                                                                                                                                             |

| 0 V            | 3   | Power contact 0 V (internally connected to terminal point 7)                                                                                                                                  |

| С              | 4   | Input C or                                                                                                                                                                                    |

|                |     | zero input (in case bit 0 (EnLatchC [ > 33]) is set in the control byte, a rising edge at this input causes the current counter value to be saved in the latch register as a reference mark). |

| В              | 5   | Input B                                                                                                                                                                                       |

| +24 V          | 6   | Power contact +24 V                                                                                                                                                                           |

| 0 V            | 7   | Power contact 0 V (internally connected to terminal point 3)                                                                                                                                  |

| Gate/Latch     | 8   | Gate input or Latch input: if  • bit 3 (EnLatchRise [▶ 33]) is set in the control byte, a rising edge  • bit 4 (EnLatchFall [▶ 33]) is set in the control byte, a falling edge                |

|                |     | at this input causes the current counter value to be saved in the latch register as a reference mark.                                                                                         |

# 4.5 KL5152-0000 (KL5151-0050) - Connection

#### Risk of injury through electric shock and damage to the device!

Bring the Bus Terminals system into a safe, de-energized state before starting mounting, disassembly or wiring of the Bus Terminals.

Fig. 13: KL5151-0050

#### Pin assignment

| Terminal point | No. | Connection for                                                 |

|----------------|-----|----------------------------------------------------------------|

| A1             | 1   | Input A for encoder 1                                          |

| +24 V          | 2   | Power contact +24 V (internally connected to terminal point 6) |

| 0 V            | 3   | Power contact 0 V (internally connected to terminal point 7)   |

| A2             | 4   | Input A for encoder 2                                          |

| B1             | 5   | Input B for encoder 1                                          |

| +24 V          | 6   | Power contact +24 V (internally connected to terminal point 2) |

| 0 V            | 7   | Power contact 0 V (internally connected to terminal point 3)   |

| B2             | 8   | Input B for encoder 2                                          |

# 4.6 ATEX - Special conditions

Observe the special conditions for the intended use of Beckhoff fieldbus components in potentially explosive areas (directive 94/9/EU)!

- ✓ Conditions

- a) The certified components are to be installed in a suitable housing that guarantees a protection class of at least IP54 in accordance with EN 60529! The environmental conditions during use are thereby to be taken into account!

- b) If the temperatures during rated operation are higher than 70°C at the feed-in points of cables, lines or pipes, or higher than 80°C at the wire branching points, then cables must be selected whose temperature data correspond to the actual measured temperature values!

- c) Observe the permissible ambient temperature range of 0 55°C for the use of Beckhoff fieldbus components in potentially explosive areas!

- d) Measures must be taken to protect against the rated operating voltage being exceeded by more than 40% due to short-term interference voltages!

- e) The individual terminals may only be unplugged or removed from the Bus Terminal system if the supply voltage has been switched off or if a non-explosive atmosphere is ensured!

- f) The connections of the certified components may only be connected or disconnected if the supply voltage has been switched off or if a non-explosive atmosphere is ensured!

- g) The fuses of the KL92xx/EL92xx power feed terminals may only be exchanged if the supply voltage has been switched off or if a non-explosive atmosphere is ensured!

- h) Address selectors and ID switches may only be adjusted if the supply voltage has been switched off or if a non-explosive atmosphere is ensured!

#### **Standards**

The fundamental health and safety requirements are fulfilled by compliance with the following standards:

Version: 2.0.0

• EN 60079-0: 2006

• EN 60079-15: 2005

#### Marking

The Beckhoff fieldbus components certified for potentially explosive areas bear one of the following markings:

II 3 G Ex nA II T4 KEMA 10ATEX0075 X Ta: 0 - 55°C

or

II 3 G Ex nA nC IIC T4 KEMA 10ATEX0075 X Ta: 0 - 55°C

## 4.7 ATEX Documentation

Note

Notes about operation of the Beckhoff terminal systems in potentially explosive areas (ATEX)

Pay also attention to the continuative documentation Notes about operation of the Beckhoff terminal systems in potentially explosive areas (ATEX) that is available in the download area of the Beckhoff homepage <a href="http://www.beckhoff.com">http://www.beckhoff.com</a>!

# 5 Configuration software KS2000

#### 5.1 KS2000 - Introduction

The KS2000 configuration software permits configuration, commissioning and parameterization of bus couplers, of the affiliated bus terminals and of Fieldbus Box Modules. The connection between bus coupler / Fieldbus Box Module and the PC is established by means of the serial configuration cable or the fieldbus.

Fig. 14: KS2000 configuration software

#### Configuration

You can configure the Fieldbus stations with the Configuration Software KS2000 offline. That means, setting up a terminal station with all settings on the couplers and terminals resp. the Fieldbus Box Modules can be prepared before the commissioning phase. Later on, this configuration can be transferred to the terminal station in the commissioning phase by means of a download. For documentation purposes, you are provided with the breakdown of the terminal station, a parts list of modules used and a list of the parameters you have modified. After an upload, existing fieldbus stations are at your disposal for further editing.

#### **Parameterization**

KS2000 offers simple access to the parameters of a fieldbus station: specific high-level dialogs are available for all bus couplers, all intelligent bus terminals and Fieldbus Box modules with the aid of which settings can be modified easily. Alternatively, you have full access to all internal registers of the bus couplers and intelligent terminals. Refer to the register description for the meanings of the registers.

#### Commissioning

The KS2000 software facilitates commissioning of machine components or their fieldbus stations: Configured settings can be transferred to the fieldbus modules by means of a download. After a *login* to the terminal station, it is possible to define settings in couplers, terminals and Fieldbus Box modules directly *online*. The same high-level dialogs and register access are available for this purpose as in the configuration phase.

The KS2000 offers access to the process images of the bus couplers and Fieldbus Box modules.

- Thus, the coupler's input and output images can be observed by monitoring.

- Process values can be specified in the output image for commissioning of the output modules.

All possibilities in the *online mode* can be used in parallel with the actual fieldbus mode of the terminal station. The fieldbus protocol always has the higher priority in this case.

24

#### 5.2 Parameterization with KS2000

Connect the configuration interface of your fieldbus coupler with the serial interface of your PC via the configuration cable and start the *KS2000* configuration software.

Click on the *Login* button. The configuration software will now load the information for the connected fieldbus station.

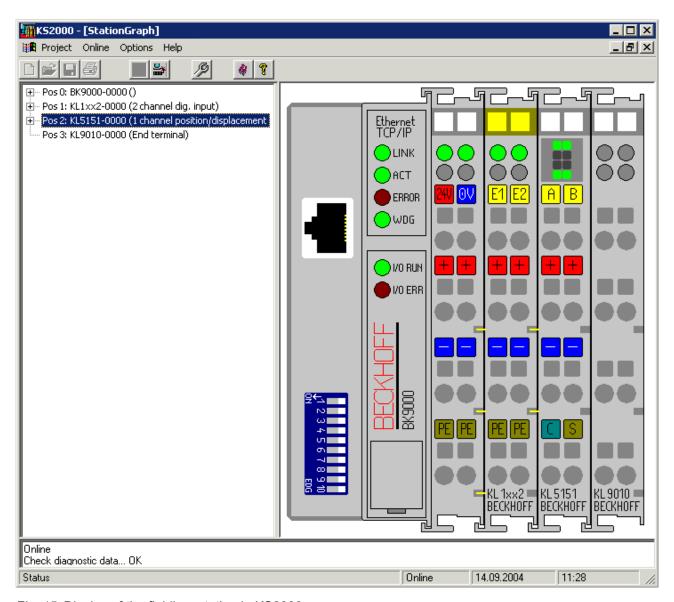

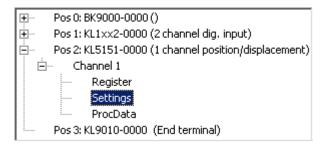

In the example shown, this is

- · a BK9000 Ethernet coupler

- · a KL1xx2 digital input terminal

- · a KL5151-0000 incremental encoder terminal

- · a KL9010 bus end terminal

Fig. 15: Display of the fieldbus station in KS2000

The left-hand KS2000 window displays the terminals of the fieldbus station in a tree structure. The right-hand KS2000 window contains a graphic display of the fieldbus station terminals.

In the tree structure of the left-hand window, click on the plus-sign next to the terminal whose parameters you wish to change (item 2 in the example).

Fig. 16: KS2000 tree branches for channel 1 of the KL5151

For the KL5151, the branches *Register*, *Settings* and *ProcData* are displayed:

- · Register permits direct access to the registers of the KL5151.

- Under <u>Settings</u> [▶ 26] you find dialog boxes for parameterizing the KL5151.

- · ProcData displays the KL5151 process data.

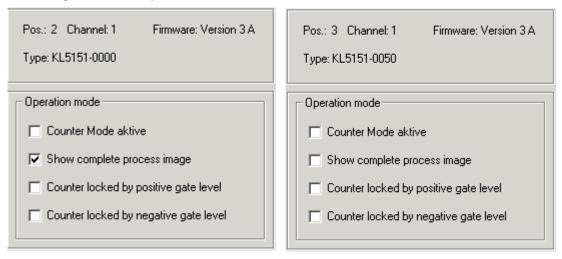

# 5.3 Settings

The dialog mask for the parameterization of the KL5151-0000 or KL5151-0050 can be found under Settings.

Fig. 17: Settings via KS2000

#### **Operation mode**

#### Counter mode active (R32.15 [▶ 46])

You can activate counter mode here (default: inactive). When counter mode is activated, the KL5151-0000 operates as a 32 bit up/down counter.

#### Display whole process image (R32.6 [▶ 46])

Meaningful operation of the KL5151-0000 is only possible with the full process image (default: active)!

The KL5151-0050 is factory-set to the small (compact) process image. You can activate evaluation of the full process image for the KL5151-0050 here.

#### A positive level at the gate locks the counter (R32.5 [> 46])

You can lock the counter by applying a positive level to the gate input (default: inactive).

# A negative level at the gate locks the counter (R32.4 [▶ 46])

You can lock the counter by applying a negative level to the gate input (default: inactive).

# 6 Access from the user program

#### 6.1 KL5151-0000

#### 6.1.1 Process image

In the process image, the KL5151 is represented with 5 bytes of input and output data. These are organized as follows:

| Format         | Input data | Output data |

|----------------|------------|-------------|

| Byte           | SB [▶ 30]  | CB [▶ 29]   |

| Double<br>word | DataIN     | DataOUT     |

#### Legend

SB: Status byte CB: Control byte

DatalN: The current value of the 32-bit counter, or the one stored in the latch (the selection is made with bit CB1.1 [> 29] of the control byte)

DataOUT: Value specified for the 32 bit counter

- Please refer to the <u>Mapping [▶ 31]</u> page for the allocation of the bytes and words to the addresses of the controller.

- The meaning of the control and status bytes is explained on the Control and Status bytes [▶ 29] page.

Version: 2.0.0

#### Note

#### No compact process image

Operation of the KL5151-0000 with compact process image (without control and status bytes) is not possible, since the control and status bytes are required for useful process data operation of the terminal. Even if you adjust your Bus Coupler to the compact process image, the KL5151-0000 will still be represented with its complete process image!

# 6.1.2 Control and status bytes

#### **Channel 1**

#### Process data mode

#### Control byte 1 in process data mode

Control byte 1 (CB1) is located in the output image, and is transmitted from the controller to the terminal.

| Bit  | CB1.7     | CB1.6 | CB1.5          | CB1.4       | CB1.3       | CB1.2  | CB1.1     | CB1.0    |

|------|-----------|-------|----------------|-------------|-------------|--------|-----------|----------|

| Name | RegAccess | -     | RS_CNT_L<br>AT | EnLatchFall | EnLatchRise | SetCnt | ReadLatch | EnLatchC |

#### Legend

| Bit   | Name            | Description      |                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|-------|-----------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CB1.7 | RegAccess       | O <sub>bin</sub> | Register communication off (process data mode)                                                                                                                                                                                                                                                      |  |  |  |  |

| CB1.6 | -               | reserved         |                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| CB1.5 | RS_CNT_LA<br>T* | 1 <sub>bin</sub> | The counter is set to zero by an active edge at the <u>latch input</u> [▶ 18]. Bits CB1.4, CB1.3 and CB1.0 specify which edge of the latch signal is active.                                                                                                                                        |  |  |  |  |

| CB1.4 | EnLatchFall*    | 1 <sub>bin</sub> | The falling edge of the <u>latch input [▶ 18]</u> is active. The counter value is stored in the latch register at the first external latch impulse after the EnLatchFall bit becomes true. The subsequent pulses do not have any effect on the latch register.                                      |  |  |  |  |

| CB1.3 | EnLatchRise *   | 1 <sub>bin</sub> | The rising edge of the <u>latch input [&gt; 18]</u> is active. The counter value is stored in the latch register on the first external latch pulse after the EnLatchRise bit becomes true (this has priority over EnLatchFall). The subsequent pulses do not have any effect on the latch register. |  |  |  |  |

| CB1.2 | SetCnt          |                  | t SetCnt will set the counter to the 32 bit value that is written by to the process output data.                                                                                                                                                                                                    |  |  |  |  |

| CB1.1 | ReadLatch       | O <sub>bin</sub> | The current value of the 32 bit counter is mapped to the process input data.                                                                                                                                                                                                                        |  |  |  |  |

|       |                 | 1 <sub>bin</sub> | The 32 bit value stored in the latch counter is mapped to the process input data.                                                                                                                                                                                                                   |  |  |  |  |

| CB1.0 | EnLatchC*       | 1 <sub>bin</sub> | The rising edge of the zero input (input C [▶ 18]) is active. The counter value is stored in the latch register at the first external latch impulse after the EnLatchC bit becomes true. The subsequent pulses do not have any effect on the latch register. (see note below)                       |  |  |  |  |

<sup>\*)</sup> Does not apply to KL5152-0000 (KL5151-0050), since the latch input and zero input are not available in this case. Always set bits CB1.5, CB1.4, CB1.3 and CB1.0 of the KL5152-0000 (KL5151-0050) to  $0_{\rm bin}$ !

#### EnLatchC or EnLatchRise and EnLatchFall?

If bit CB1.0 (EnLatchC) is set, bit CB1.3 (EnLatchRise) and bit CB1.4 (EnLatchFall) must not be set, otherwise you cannot know which event has caused a counter value to be stored in the latch.

#### Status byte 1 in process data mode

The status byte 1 (SB1) is located in the input image, and is transmitted from terminal to the controller.

| Bit  | SB1.7    | SB1.6 | SB1.5 | SB1.4  | SB1.3    | SB1.2  | SB1.1    | SB1.0     |

|------|----------|-------|-------|--------|----------|--------|----------|-----------|

| Name | RegAcces | -     | -     | StGate | StLatchC | SetCnt | ReadLatc | ValLatchC |

|      | s        |       |       |        |          |        | h        |           |

## Legend

| Bit   | Name       | Description                |                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|-------|------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| SB1.7 | RegAccess  | O <sub>bin</sub>           | Acknowledgement for process data mode                                                                                                                                                                                                                                                                |  |  |  |  |  |

| SB1.6 | -          | reserved                   |                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| SB1.5 | -          | reserved                   |                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| SB1.4 | StGate     | KL5151-0000:               | Status of the external gate/latch input [▶ 18]                                                                                                                                                                                                                                                       |  |  |  |  |  |

|       |            | KL5152-0000                | (KL5151-0050): reserved                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| SB1.3 | StLatchC   | KL5151-0000:               | Status of the zero input (input C [▶ 18])                                                                                                                                                                                                                                                            |  |  |  |  |  |

|       |            | KL5152-0000                | (KL5151-0050): reserved                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| SB1.2 | SetCnt     | Acknowledgen the terminal. | nent that the data for setting the counter has been adopted by                                                                                                                                                                                                                                       |  |  |  |  |  |

| SB1.1 | ReadLatch  | O <sub>bin</sub>           | The current value of the 32 bit counter has been mapped to the process data.                                                                                                                                                                                                                         |  |  |  |  |  |

|       |            | 1 <sub>bin</sub>           | The 32 bit value stored in the latch counter has been mapped to the process data.                                                                                                                                                                                                                    |  |  |  |  |  |

| SB1.0 | ValLatchC* | 1 <sub>bin</sub>           | A zero-point latch has occurred: a rising edge at the zero input (input C [ > 18]) has caused the current counter value to be stored in the latch register as a reference mark. Subsequent pulses do not have any effect on the latch register. To reactivate the gate/latch input [ > 18] you must: |  |  |  |  |  |

|       |            |                            | <ul> <li>set bit 0 (EnLatchC) in the control byte to 0<sub>bin</sub>.</li> </ul>                                                                                                                                                                                                                     |  |  |  |  |  |

|       |            |                            | <ul> <li>wait until this change has been acknowledged by<br/>resetting bit 0 (ValLatchC) in the status byte.</li> </ul>                                                                                                                                                                              |  |  |  |  |  |

|       |            |                            | <ul> <li>set bit 0 (EnLatchC) in the control byte to 1<sub>bin</sub> again.</li> </ul>                                                                                                                                                                                                               |  |  |  |  |  |

<sup>\*)</sup> Does not apply to KL5152-0000 (KL5151-0050), since the latch input and zero input are not available in this case.

# **Register communication**

#### Control byte 1 in register communication

Control byte 1 (CB1) is located in the output image, and is transmitted from the controller to the terminal.

| Bit  | CB1.7     | CB1.6 | CB1.5    | CB1.4 | CB1.3 | CB1.2 | CB1.1 | CB1.0 |

|------|-----------|-------|----------|-------|-------|-------|-------|-------|

| Name | RegAccess | R/W   | Reg. no. |       |       |       |       |       |

# Legend

| Bit      | Name      | Description                  |                                                                                          |  |  |  |  |

|----------|-----------|------------------------------|------------------------------------------------------------------------------------------|--|--|--|--|

| CB1.7    | RegAccess | 1 <sub>bin</sub>             | Register communication switched on                                                       |  |  |  |  |

| CB1.6    | R/W       | 0 <sub>bin</sub> Read access |                                                                                          |  |  |  |  |

|          |           | 1 <sub>bin</sub>             | Write access                                                                             |  |  |  |  |

| CB1.5 to | Reg. no.  | Register number              | er:                                                                                      |  |  |  |  |

| CB1.0    |           | - want to read \             | per of the <u>register [▶ 44]</u> that you with input data word 0 or putput data word 0. |  |  |  |  |

#### No valid process data during the register communication!

It is not possible to access the data registers during register communication! Process data that may still be displayed is not valid!

#### Status byte 1 in register communication

The status byte 1 (SB1) is located in the input image, and is transmitted from terminal to the controller.

| Bit  | SB1.7     | SB1.6 | SB1.5    | SB1.4 | SB1.3 | SB1.2 | SB1.1 | SB1.0 |

|------|-----------|-------|----------|-------|-------|-------|-------|-------|

| Name | RegAccess | R     | Reg. no. |       |       |       |       |       |

#### Legend

| Bit               | Name      | Description      |                                     |

|-------------------|-----------|------------------|-------------------------------------|

| SB1.7             | RegAccess | 1 <sub>bin</sub> | Acknowledgement for register access |

| SB1.6             | R         | O <sub>bin</sub> | Read access                         |

| SB1.5 to<br>SB1.0 | Reg. no.  | Number of the    | register that was read or written.  |

#### Channel 2 (KL5152-0000 and KL5151-0050 only)

The control and status bytes of channel 2 (CB2 and SB2) have the same structure as the control and status bytes of channel 1 [▶ 29].

# 6.1.3 Mapping

The Bus Terminals occupy addresses within the process image of the controller. The assignment of process data (input and output data) and parameterization data (control and status bytes) to the control addresses is called mapping. The type of mapping depends on:

- · the fieldbus system used

- · the terminal type

- · the parameterization of the Bus Coupler such as

- Intel or Motorola format

- word alignment switched on or off

The Bus Couplers (BKxxxx, LCxxxx) and Bus Terminal Controllers (BCxxxx, BXxxxx) are supplied with certain default settings. The default setting can be changed with the KS2000 configuration software or with a master configuration software (e.g. TwinCAT System Manager or ComProfibus).

The following tables show the mapping depending on different conditions. For information about the contents of the individual bytes please refer to the pages <u>Process image</u> [▶ 28] and <u>Control and status byte</u> [▶ 29].

#### Complete evaluation

Control and status bytes can be accessed.

#### Complete evaluation in Intel format

Default mapping for CANopen, CANCAL, DeviceNet, ControlNet, Modbus, RS232 and RS485 coupler.

| Parameterization         | Address     | Input data |           | Output data |            |  |

|--------------------------|-------------|------------|-----------|-------------|------------|--|

| of the Bus Coupler       | Word offset | High byte  | Low byte  | High byte   | Low byte   |  |

| Complete evaluation: n/a | 0           | DataIN D0  | SB        | DataOUT D0  | СВ         |  |

| Motorola format: no      | 1           | DataIN D2  | DataIN D1 | DataOUT D2  | DataOUT D1 |  |

| Word alignment: no       | 2           | reserved   | DataIN D3 | reserved    | DataOUT D3 |  |

#### **Complete evaluation in Motorola format**

| Parameterization         | Address     | Input data |           | Output data |            |  |

|--------------------------|-------------|------------|-----------|-------------|------------|--|

| of the Bus Coupler       | Word offset | High byte  | Low byte  | High byte   | Low byte   |  |

| Complete evaluation: n/a | 0           | DataIN D3  | SB        | DataOUT D3  | СВ         |  |

| Motorola format: yes     | 1           | DataIN D1  | DataIN D2 | DataOUT D1  | DataOUT D2 |  |

| Word alignment: no       | 2           | reserved   | DataIN D0 | reserved    | DataOUT D0 |  |

#### Complete evaluation in Intel format with word alignment

Default mapping for EtherCAT, Lightbus and Ethernet coupler as well as Bus Terminal Controllers (BCxxxx, BXxxxx).

| Parameterization         | Address     | Input data |           | Output data |            |  |

|--------------------------|-------------|------------|-----------|-------------|------------|--|

| of the Bus Coupler       | Word offset | High byte  | Low byte  | High byte   | Low byte   |  |

| Complete evaluation: n/a | 0           | reserved   | SB        | reserved    | СВ         |  |

| Motorola format: no      | 1           | DataIN D1  | DataIN D0 | DataOUT D1  | DataOUT D0 |  |

| Word alignment: yes      | 2           | DataIN D3  | DataIN D2 | DataOUT D3  | DataOUT D2 |  |

#### Complete evaluation in Motorola format with word alignment

| Parameterization         | Address     | Input data |           | Output data |            |  |

|--------------------------|-------------|------------|-----------|-------------|------------|--|

| of the Bus Coupler       | Word offset | High byte  | Low byte  | High byte   | Low byte   |  |

| Complete evaluation: n/a | 0           | reserved   | SB1       | reserved    | CB1        |  |

| Motorola format: yes     | 1           | DataIN D2  | DataIN D3 | DataOUT D2  | DataOUT D3 |  |

| Word alignment: yes      | 2           | DataIN D0  | DatalN D1 | DataOUT D0  | DataOUT D1 |  |

#### Legend

Complete evaluation: In addition to the process data, the control and status bytes are also mapped into the address space.

Motorola format: Motorola or Intel format can be set.

Word alignment: In order for the word address range to commence at a word boundary, empty bytes are inserted into the process image as appropriate.

SB: Status byte (appears in the input process image)

CB: Control byte (appears in the output process image)

DataIN D0: Input double word, lowest significant data byte

DataIN D1: Input double word, ... DataIN D2: Input double word, ...

DataIN D3: Input double word, highest significant data byte

DataOUT D0: Output double word, lowest significant data byte

DataOUT D1: Output double word, ... DataOUT D2: Output double word, ...

DataOUT D3: Output double word, highest significant data byte

reserved: This byte occupies process data memory, although it has no function.

#### Compact evaluation

#### No compact process image

Operation of the KL5151-0000 with compact process image (without control and status bytes) is not possible, since the control and status bytes are required for useful process data operation of the terminal. Even if you adjust your Bus Coupler to the compact process image, the KL5151-0000 will still be represented with its complete process image!

#### 6.2 KL5151-0021

#### 6.2.1 Process image

In the process image, the KL5151 is represented with 5 bytes of input and output data. These are organized as follows:

| Format      | Input data | Output data |

|-------------|------------|-------------|

| Byte        | SB1 [▶ 33] | CB1 [▶ 33]  |

| Double word | DataIN1    | DataOUT1    |

| Byte        | SB2        | CB2         |

| Double word | DataIN2    | DataOUT2    |

#### Legend

SB1: Status byte 1 CB1: Control byte 1

SB1: Status byte 2 (not used) CB1: Control byte 2 (not used)

DatalN1: The current value of the 32-bit counter, or the one stored in the latch (the selection is made with bit CB1.1 [> 33] of the control byte)

DataOUT1: Compare value for setting the comparator output (enabled by bit <u>CB1.6 [▶ 33]</u> of the control

byte).

DataIN2: 32-bit latch

DataOUT2: Compare value for resetting the comparator output

• The meaning of the control and status bytes is explained on the Control and Status bytes [ > 33] page.

#### No compact process image

Operation of the KL5151-0021 with compact process image (without control and status bytes) is not possible, since the control and status bytes are required for useful process data operation of the terminal. Even if you adjust your Bus Coupler to the compact process image, the KL5151-0021 will still be represented with its complete process image!

# 6.2.2 Control and status bytes

#### Control byte 1 and status byte 1

#### Process data mode

#### Control byte 1 in process data mode

Control byte 1 (CB1) is located in the output image, and is transmitted from the controller to the terminal.

| Bit  | CB1.7     | CB1.6  | CB1.5  | CB1.4      | CB1.3      | CB1.2  | CB1.1  | CB1.0    |

|------|-----------|--------|--------|------------|------------|--------|--------|----------|

| Name | RegAccess | EnComp | SetOut | ReadLatchN | ReadLatchP | SetCnt | EnMeas | EnLatchC |

#### Legend

| Bit   | Name       | Desci            | iption                                                                                                                                                                                                                                                                        |                                                                   |  |  |  |  |

|-------|------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--|--|--|--|

| CB1.7 | RegAccess  | O <sub>bin</sub> | Register communication off (p                                                                                                                                                                                                                                                 | Register communication off (process data mode)                    |  |  |  |  |

| CB1.6 | EnComp     | O <sub>bin</sub> | Compare function for setting a                                                                                                                                                                                                                                                | Compare function for setting and resetting the output not enabled |  |  |  |  |

|       |            | 1 <sub>bin</sub> | Compare function for setting a                                                                                                                                                                                                                                                | and resetting the output enabled                                  |  |  |  |  |

| CB1.5 | SetOut     | O <sub>bin</sub> | sets output manually to 0 V                                                                                                                                                                                                                                                   | SetOut only functions if EnComp =                                 |  |  |  |  |

|       |            | 1 <sub>bin</sub> | sets output manually to 24 V                                                                                                                                                                                                                                                  | $0_{bin}$                                                         |  |  |  |  |

| CB1.4 | ReadLatchN | 1 <sub>bin</sub> | Read the negative edge                                                                                                                                                                                                                                                        | Read the negative edge                                            |  |  |  |  |

| CB1.3 | ReadLatchP | 1 <sub>bin</sub> | Read the positive edge                                                                                                                                                                                                                                                        | Read the positive edge                                            |  |  |  |  |

| CB1.2 | SetCnt     |                  | ng edge at SetCnt will set the cone controller into the process outp                                                                                                                                                                                                          | unter to the 32 bit value that is written ut data.                |  |  |  |  |

| CB1.1 | EnMeas     | O <sub>bin</sub> | Workpiece measurement enabled                                                                                                                                                                                                                                                 | If the workpiece measurement is enabled, it is read via CB1.3 and |  |  |  |  |

|       |            | 1 <sub>bin</sub> | Workpiece measurement not enabled                                                                                                                                                                                                                                             | CB1.4 and saved in two latch values.                              |  |  |  |  |

| CB1.0 | EnLatchC   | 1 <sub>bin</sub> | The rising edge of the zero input (input C [▶ 19]) is active. The counter value is stored in the latch register at the first external latch impulse after the EnLatchC bit becomes true. The subsequent pulses do not have any effect on the latch register. (see note below) |                                                                   |  |  |  |  |

#### **EnLatchC or EnLatchRise and EnLatchFall?**

If bit CB1.0 (EnLatchC) is set, bit CB1.3 (EnLatchRise) and bit CB1.4 (EnLatchFall) must not be set, otherwise you cannot know which event has caused a counter value to be stored in the latch.

#### Status byte 1 in process data mode

The status byte 1 (SB1) is located in the input image, and is transmitted from terminal to the controller.

| Bit  | SB1.7     | SB1.6 | SB1.5 | SB1.4  | SB1.3    | SB1.2  | SB1.1    | SB1.0     |

|------|-----------|-------|-------|--------|----------|--------|----------|-----------|

| Name | RegAccess | -     | StOut | StGate | StLatchC | SetCnt | MeasDone | ValLatchC |

#### Legend

| Bit   | Name      | Descri                                                                                  | ption                                                                                                                                                                                                                                                                                                 |  |  |

|-------|-----------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|